Synchronous D flipflop:

--library declaration for the module. library ieee; use ieee.std_logic_1164.all; --This is a D Flip-Flop with Synchronous Reset,Set and Clock Enable(posedge clk). --Note that the reset input has the highest priority,Set being the next highest --priority and clock enable having the lowest priority. entity FDRSE1 is port(Clk :in std_logic; -- Clock input ce :in std_logic; -- Clock enable input reset :in std_logic; -- Synchronous reset input D :in std_logic; -- Data input set : in std_logic; -- Synchronous set input Q : out std_logic -- Data output ); end FDRSE1; architecture behavioral of FDRSE1 is --architecture of the circuit. begin --"begin" statement for architecture. process(Clk) --process with sensitivity list. begin --"begin" statment for the process. if(rising_edge(Clk)) then --This makes the process synchronous(with clock) if(reset = '1') then --synchronous reset, highest priority Q <= '0'; else if(set = '1') then --synchronous set, next priority Q <= '1'; else if(ce = '1') then --clock enable, lowest priority Q <= D; end if; end if; end if; end if; end process; --end of process statement. end behavioral;

Testbench Code for the D flipflop:

library ieee; use ieee.std_logic_1164.all; --testbench has empty entity entity tb_FDRSE is end entity tb_FDRSE; architecture behavioral of tb_FDRSE is signal Clk,reset,ce,Q,D,set : std_logic := '0'; constant Clk_period : time := 10 ns; begin --entity instantiation with named association port mapping FDRSE_uut: entity work.FDRSE1 port map(Clk => Clk, ce => ce, reset => reset, D => D, set => set, Q => Q); --generate clock Clk_generation: process begin wait for Clk_period/2; Clk <= not Clk; --toggle clock when half of clk_period is over end process; stimulus: process begin ce <= '1'; D <= '1'; set <= '0'; reset <= '0'; wait for Clk_period; D <= '0'; wait for Clk_period; D <= '1'; wait for Clk_period; reset <= '1'; wait for Clk_period; reset <= '0'; wait for Clk_period; set <= '1'; wait for Clk_period; set <= '0'; D <= '0'; wait for Clk_period; ce <= '0'; D <= '1'; wait for Clk_period; wait; --testing done. wait endlessly end process; end behavioral;

Simulation Waveform from Modelsim:

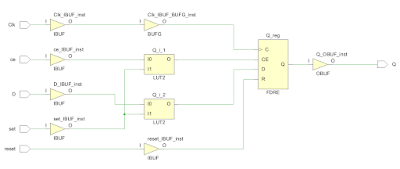

Schematic from Xilinx Vivado after Synthesis:

Note :- This flipflop entity is named with a "1" at the end because the name "FDRSE" stands for a primitive component in Xilinx FPGAs which creates a synthesis error. You can see from the schematic that apart from few logic gates, the only flipflop used is called FDRE.

test bench?????

ReplyDelete@awais : I left the testbench for this module as an exercise to students. Read this post and write a similar testbench.

ReplyDeletehttp://vhdlguru.blogspot.com/2010/03/positive-edge-triggered-jk-flip-flop.html

Hi all !!

ReplyDeleteI have a flip-flop that I need to enable for only one clock cycle. What is the standard practice for single-cycle enable signal in these kind of situations?

please write program for d ff for symmetric in reset clk and only

ReplyDeleteTHAT IS HELPFUL,THANKS

ReplyDeleteClear and preset are independent of the clock signal

ReplyDelete