VHDL Code for 4:1 MUX:

--library declarations. library ieee; use ieee.std_logic_1164.all; entity multiplexer4_1 is port(i0 : in std_logic; --input wire 1 i1 : in std_logic; --input wire 2 i2 : in std_logic; --input wire 3 i3 : in std_logic; --input wire 4 sel : in std_logic_vector(1 downto 0); --select input bitout : out std_logic --output ); end multiplexer4_1; architecture Behavioral of multiplexer4_1 is begin --make sure to include all signals in the process sensitivity list which affects the output. --The below process contains the behavioral description of 4:1 MUX. process(i0,i1,i2,i3,sel) begin case sel is when "00" => bitout <= i0; when "01" => bitout <= i1; when "10" => bitout <= i2; when others => bitout <= i3; end case; end process; end Behavioral;

Testbench code for 4:1 MUX:

--library declarations library ieee; use ieee.std_logic_1164.all; --testbench entity is always empty. no ports to be declared here. entity testbench is end testbench; architecture behavior of testbench is --internal signals signal i0,i1,i2,i3,bitout : std_logic:='0'; signal sel : std_logic_vector(1 downto 0):="00"; begin --entity instantiation with named association style mux_4_1 : entity work.multiplexer4_1 port map(i0 => i0, i1 => i1, i2 => i2, i3 => i3, sel => sel, bitout => bitout); stimulus : process begin --set the four input lines i0<='1'; i1<='0'; i2<='1'; i3<='0'; --wait for 2 ns after changing 'select' input each time, --so that we can see the change in simulation waveform sel <="00"; wait for 2 ns; sel <="01"; wait for 2 ns; sel <="10"; wait for 2 ns; sel <="11"; wait for 2 ns; --more input combinations can be given here. wait; end process stimulus; end;

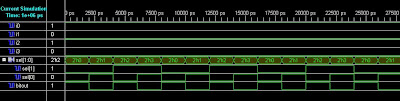

Simulation Waveform:

The codes were simulated in Xilinx ISE. This is a screenshot of the waveform

RTL Schematic:

The code was successfully synthesized in Xilinx ISE. The RTL schematic of the design is shown below.

Note :- Use RTL Viewer to get a closer look on how your design is actually implemented in hardware.

Note :- Use RTL Viewer to get a closer look on how your design is actually implemented in hardware.

Note2 :- You might have seen my blog article, why you should use signed/unsigned data types instead of std_logic_vector(SLV). But here the sel input is declared as std_logic_vector. You might be wondering, why?

This was a deliberate decision. The idea is not to completely abandon SLV, but use it only for signals of general purpose, where you don't need to perform any logical or arithmetical operations on them.

can you please explain the dataflow model...

ReplyDeleteit's very easy but how I write code for 8 bits multiplexer?

ReplyDeleteproblem is:

a and b 8 bot input, c is 2 bit input , D is 8bit output if c="00" output A, c="01" output B, c="10" output D, c="11" output Z

help me how I write Its code

What is the difference between your architecture code and the following one from synthesis point of view?

ReplyDeleteIn case of pure combinational logic (like the described multiplexer) why a process with all the inputs in the sensitivity list should be used instead of the version below?

maybe its the same, or maybe I miss some important difference between the two different descriptions!

thanks!

architecture Behavioral of multiplexer4_1 is

begin

bitout <= i0 when sel="00" else

i1 when sel="01" else

i2 when sel="10" else

i3 ;

end Behavioral;

actually your syntext is totally wrong...either use elsif.or use other architecture....

ReplyDeleteprogramme vhdl d'un multiplexeur 4-1 en utilisant 2 demi multiplexeurs

ReplyDeletei am a beginner to vhdl..... Can u explain how i can see the rtl schematic in the form of AND , XOR..... i get them as mere boxes with corresponding inputs and outputs........

ReplyDeleteThe code was nice

ReplyDeleteIs there any problem if I use signal sel : std_logic_vector(1 downto 0);

ReplyDeleteAfter the begin of architecture line

ERROR: The Top module has not been specified. This can happen if no sources have been added to the project,

ReplyDeleteGetting the above error. Can you please help me out on this ?